# <u>Preliminary</u>

EUP2618

# Triple Adjustable Output TFT-LCD DC-DC Converters

#### **DESCRIPTION**

MICROFI ECTRONICS

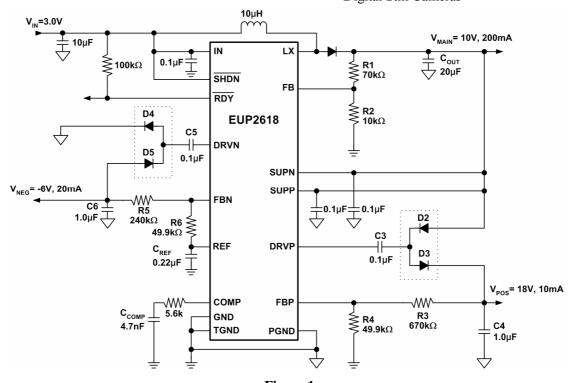

The EUP2618 triple-output DC-DC converter provides the regulated voltages required by active-matrix, thin-film transistor (TFT) liquid-crystal displays (LCDs). One high-power DC-DC converter and two low-power charge pumps convert the 3.3V to 5V input supply voltage into three independent output voltages.

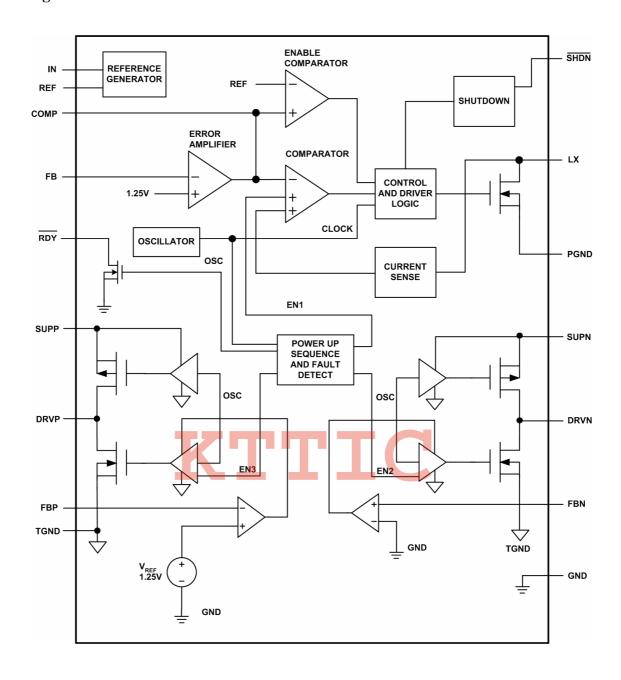

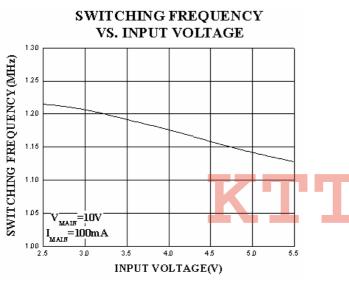

The primary 1.2MHz DC-DC converter generates a boosted output voltage ( $V_{MAIN}$ ) up to 18V using ultra-small inductors and ceramic capacitors. The low-power control circuitry and the low on-resistance (0.2 $\Omega$ ) of the integrated power MOSFET allows efficiency up to 92%.

The dual charge pumps independently regulate one positive output  $(V_{POS})$  and one negative output  $(V_{NEG})$ . These low-power outputs use external diode and capacitor stages to regulate output voltages up to 40V and down to -40V.

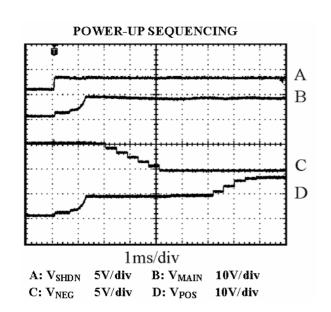

For EUP2618, the supply sequence is  $V_{MAIN}$  first,  $V_{NEG}$  next, and finally  $V_{POS}$ . The EUP2618 soft-starts each supply as soon as the previous supply finishes.

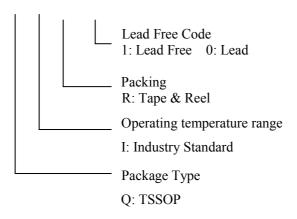

The EUP2618 are available in the ultra-thin TSSOP-16 package.

#### **FEATURES**

- 1.2MHz Current-Mode PWM Boost Regulator Up to 18V Main High-Power Output 2.1A, 0.2Ω Power MOSFET

92% High Efficiency

- Dual Adjustable Charge-Pump Outputs

Up to 40V Positive Output

Down to -40V Negative Output

- Internal Power-up Sequencing

- 2.5V to 5.5V Input Range

- 0.1µA Shutdown Current

- 0.7mA Quiescent Current

- Internal Soft-Start

- Power-Ready Output

- Ultra-Small External Components

- Thin TSSOP-16 Package

- RoHS Compliant and 100% Lead (Pb)-Free

# **Typical Application Circuit**

#### **APPLICATIONS**

- TFT Active-Matrix LCD Displays

- Passive-Matrix LCD Displays

- PDAs

- Digital Still Cameras

## **Block Diagram**

Figure 2.

# **Pin Configurations**

| Package Type | Pin Configurations |         |  |  |

|--------------|--------------------|---------|--|--|

|              | (TOP VIEW)         |         |  |  |

|              | RDY 1              | 16 PGND |  |  |

|              | FB 2               | 15 LX   |  |  |

|              | сомр 3             | 14 TGND |  |  |

| TSSOP-16     | IN 4 EUP2618       | 13 SUPP |  |  |

|              | GND 5              | 12 DRVP |  |  |

|              | REF 6              | 11 SUPN |  |  |

|              | FBP 7              | 10 DRVN |  |  |

|              | FBN 8              | 9 SHDN  |  |  |

|              |                    |         |  |  |

# **Pin Description**

| PIN | NAME | DESCRIPTION                                                                                                                                  |  |  |  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | RDY  | Active-Low, Open-Drain Output. Indicates all outputs are ready. The on-resistance is $125\Omega$ (typ).                                      |  |  |  |

| 2   | FB   | Main Boost Regulator Feedback Input. Regulates to 1.25V nominal. Connect feedback resistive divider to analog ground (GND).                  |  |  |  |

| 3   | COMP | Main Boost Compensation Network Connection.                                                                                                  |  |  |  |

| 4   | IN   | Supply Input. 2.5V to 5.5V input range. Bypass with a 0.1µF capacitor between IN and GND, as close to the pins as possible.                  |  |  |  |

| 5   | GND  | Analog Ground. Connect to power ground (PGND) underneath the IC.                                                                             |  |  |  |

| 6   | REF  | Internal Reference Bypass Terminal. Connect a 0.22µF capacitor from this terminal to analog ground (GND). External load capability to 100µA. |  |  |  |

| 7   | FBP  | Positive Charge-Pump Regulator Feedback Input. Regulates to 1.25V nominal. Connect feedback resistive divider to analog ground (GND).        |  |  |  |

| 8   | FBN  | Negative Charge-Pump Regulator Feedback Input. Regulates to 0V nominal.                                                                      |  |  |  |

| 9   | SHDN | Active-Low Logic-Level Shutdown Input. Connect SHDN to IN for normal operation.                                                              |  |  |  |

| 10  | DRVN | Negative Charge-Pump Driver Output. Output high level is $V_{SUPN}$ , and low level is TGND.                                                 |  |  |  |

| 11  | SUPN | Negative Charge-Pump Driver Supply Voltage. Bypass to TGND with a 0.1μF capacitor.                                                           |  |  |  |

| 12  | DRVP | Positive Charge-Pump Driver Output. Output high level is V <sub>SUPP</sub> , and low level is TGND.                                          |  |  |  |

| 13  | SUPP | Positive Charge-Pump Driver Supply Voltage. Bypass to TGND with a 0.1µF capacitor.                                                           |  |  |  |

| 14  | TGND | Power Ground of Charge-Pumps.                                                                                                                |  |  |  |

| 15  | LX   | Main Boost Regulator Power MOSFET n-Channel Drain. Connect output diode and output capacitor as close to PGND as possible.                   |  |  |  |

| 16  | PGND | Power Ground of Main Boost.                                                                                                                  |  |  |  |

# **Preliminary**

*EUP2618*

# **Ordering Information**

| Order Number | Package Type | Marking          | Operating Temperature range |

|--------------|--------------|------------------|-----------------------------|

| EUP2618QIR1  | TSSOP-16     | xxxxx<br>EUP2618 | -40 °C to 85°C              |

EUP2618

# KTTIC

### **Absolute Maximum Ratings**

|   | IN to GND0.3V to 6V                                      |

|---|----------------------------------------------------------|

| • | DRVN to GND0.3V to (V <sub>SUPN</sub> +0.3V)             |

| • | DRVP to GND0.3V to (V <sub>SUPP</sub> +0.3V)             |

| • | PGND ,TGND to GND ±0.3V                                  |

| • | RDY ,SUPP,SUPN to GND                                    |

| • | LX to GND0.3V to 19V                                     |

| • | COMP, $\overline{\text{SHDN}}$ ,REF, FB ,FBN, FBP to GND |

| • | Operating Temperature                                    |

| • | Junction Temperature 150°C                               |

| • | Storage Temperature                                      |

| • | Lead Temp (Soldering, 10sec) 260°C                       |

#### **Electrical Characteristics**

(Specfications in standard type face are for  $T_A$  =25 and those with **boldface type** apply over the full **Operating Temperature Range** ( $T_A$ =-40 to 85 ).  $V_{IN}$ =3.3V,  $V_{SUPP}$ = $V_{SUPN}$ =10V ,GND=PGND=TGND=0, unless otherwise noted.)

| Parameter                        | Conditions                                                                    | EUP2618 |      |      | Unit |  |

|----------------------------------|-------------------------------------------------------------------------------|---------|------|------|------|--|

| r ar ameter                      | Conditions                                                                    | Min.    | Typ. | Max. | Omt  |  |

| Operating Power                  |                                                                               |         |      |      |      |  |

| Input Supply Voltage Range       |                                                                               | 2.5     |      | 5.5  | V    |  |

| VIN Under Voltage Lockout        | Falling                                                                       | 1.9     | 2.13 | 2.35 | V    |  |

| VIN Onder voltage Lockout        | Rising                                                                        | 2       | 2.23 | 2.45 | V    |  |

| Quiescent Current                | V <sub>FB</sub> =V <sub>FBP</sub> =1.4V, V <sub>FBN</sub> =0V, not switching  |         | 0.7  | 1    | mA   |  |

| Quiescent Current                | V <sub>FB</sub> =1.1V, V <sub>FBP</sub> =1.4V, V <sub>FBN</sub> =0V switching |         | 2.1  | 4    | mA   |  |

| Shutdown Current                 | V SHDN =GND                                                                   |         | 0.1  | 10   | uA   |  |

| Thermal Shutdown                 | 15 Hysteresis                                                                 |         | 165  |      |      |  |

| Reference                        |                                                                               |         |      |      |      |  |

| Reference Voltage                | IV <sub>REF</sub> =100uA                                                      | 1.22    | 1.25 | 1.28 | V    |  |

| Line Regulation                  | IV <sub>REF</sub> =100uA, V <sub>IN</sub> =2.5~5V                             |         | 2    | 5    | mV   |  |

| Load Regulation                  | IV <sub>REF</sub> =0~100uA                                                    |         | 1    | 5    | mV   |  |

| EA (Error Amplifier)             |                                                                               |         |      |      |      |  |

| Feedback Voltage                 |                                                                               | 1.22    | 1.25 | 1.28 | V    |  |

| Input Bias Current               | V <sub>FB</sub> =1.25V                                                        |         | 100  | 200  | nA   |  |

| Feedback Voltage Line Regulation | 2.5V <v<sub>DD&lt;5.5V</v<sub>                                                |         | 0.07 | 0.15 | %/V  |  |

| Error Amp Transconductance       | ΔI=2uA                                                                        | 30      | 60   | 90   | umho |  |

| Error Amp Voltage Gain           | FB to COMP                                                                    |         | 853  |      | V/V  |  |

| Oscillator                       |                                                                               |         |      |      |      |  |

| Operating Frequency              |                                                                               | 1000    | 1200 | 1500 | kHz  |  |

| Maximum Duty                     |                                                                               | 85      | 96   |      | %    |  |

| N-Channel Switch                 |                                                                               |         |      |      |      |  |

| Switch Current Limit             | 65% Duty Cycle                                                                | 1.5     | 2.1  | 2.8  | A    |  |

## **Electrical Characteristics (continued)**

(Specfications in standard type face are for  $T_A$  =25 and those with **boldface type** apply over the full **Operating Temperature Range** ( $T_A$ =-40 to 85 ).  $V_{IN}$ =3.3V,  $V_{SUPP}$ = $V_{SUPN}$ =10V ,GND=PGND=TGND=0, unless otherwise noted.)

| Parameter                                    | Conditions              |                          | Min.  | EUP2618             |       |      |

|----------------------------------------------|-------------------------|--------------------------|-------|---------------------|-------|------|

|                                              |                         | Conditions               |       | Тур.                | Max.  | Unit |

| Switch R <sub>DSON</sub>                     | $I_{LX}=200$ mA         | I <sub>LX</sub> =200mA   |       | 0.2                 | 0.4   | Ω    |

| Switch Leakage Current                       | $V_{\rm LX}=18V$        |                          |       | 0.01                | 20    | uA   |

| <b>Control Inputs Characteristics (SHDN)</b> |                         |                          |       |                     |       |      |

| SHDN Low Threshold                           |                         |                          |       |                     | 0.8   | V    |

| SHDN High Threshold                          |                         |                          | 1.8   |                     |       | V    |

| SHDN Pin Pull Up Current                     | SHDN=GN                 | ID                       |       | 0.001               | 1     | uA   |

| Soft Start & Fault Detect Time               |                         |                          |       |                     |       |      |

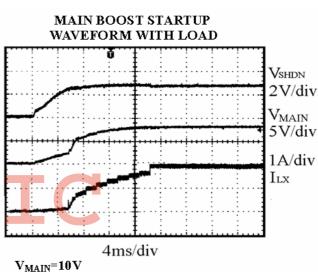

| Channel 1 Soft Start Time                    |                         |                          |       | 14                  |       | ms   |

| Channel 2 Soft Start Time                    |                         |                          |       | 3.5                 |       | ms   |

| Channel 3 Soft Start Time                    |                         |                          |       | 3.5                 |       | ms   |

| Channel 1 Fault Protect Trigger Time         |                         |                          |       | 55                  |       | ms   |

| Channel 2 Fault Protect Trigger Time         |                         |                          |       | 14                  |       | ms   |

| Channel 3 Fault Protect Trigger Time         |                         |                          |       | 14                  |       | ms   |

| FB Fault Protection Voltage                  |                         | 1                        | 1.1   | 1.2                 | V     |      |

| FBN Fault Protection Voltage                 |                         |                          | 0.08  | 0.13                | 0.18  | V    |

| FBP Fault Protection Voltage                 |                         | 1                        | 1.1   | 1.2                 | V     |      |

| Charge Pump Regulator Characteristics        |                         |                          | _     |                     |       |      |

| V <sub>SUPP</sub> Input Supply Range         |                         |                          | 5     |                     | 13.5  | V    |

| V <sub>SUPN</sub> Input Supply Range         |                         |                          | 5     |                     | 13.5  | V    |

| FBN Threshold Voltage                        |                         |                          | -50   |                     | 50    | mV   |

| FBP Threshold Voltage                        |                         |                          | 1.208 | 1.258               | 1.308 | V    |

| FBN Input Bias Current                       | $V_{FBN}$ =-0.05V       |                          | -50   |                     | 50    | nA   |

| FBP Input Bias Current                       | V <sub>FBP</sub> =-1.5V |                          | -50   |                     | 50    | nA   |

| Charge Pump Frequency                        |                         |                          |       | f <sub>OSC</sub> /2 |       | kHz  |

|                                              | PMOS                    | I <sub>OUT2</sub> =10mA  |       | 3                   | 20    |      |

| OUT2 Switch R-on                             | NMOS                    | I <sub>OUT2</sub> =-10mA |       | 3                   | 20    |      |

| OVER G. S. I. D.                             | PMOS                    | I <sub>OUT3</sub> =10mA  |       | 3                   | 20    |      |

| OUT3 Switch R-on                             | NMOS                    | I <sub>OUT3</sub> =-10mA |       | 3                   | 20    |      |

| Continuous Output Current                    | Test Condit             | tion T <sub>A</sub> =25  |       |                     | 30    | mA   |

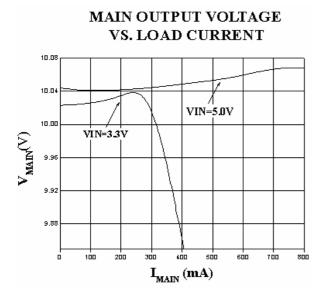

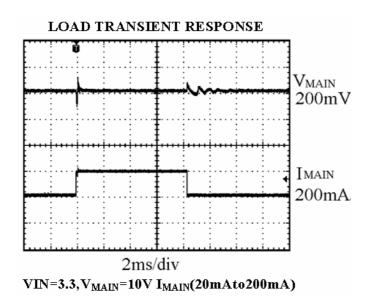

### **Typical Characteristics**

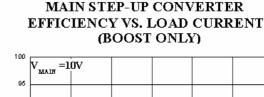

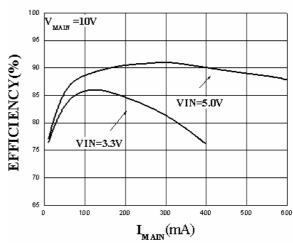

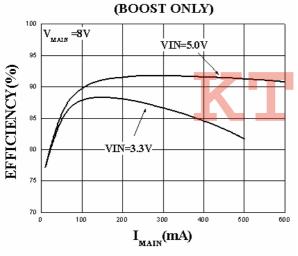

MAIN STEP-UP CONVERTER EFFICIENCY VS. LOAD CURRENT (BOOST ONLY)

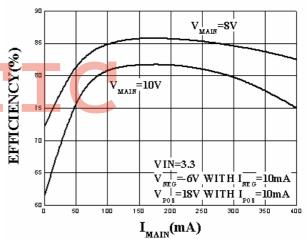

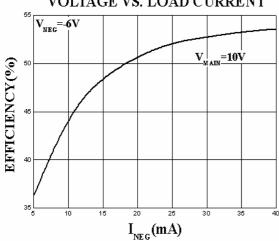

## EFFICIENCY VS.LOAD CURRENT (BOOST CONVERTER AND CHARGE PUMPS)

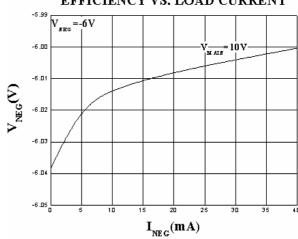

VOLTAGE VS. LOAD CURRENT

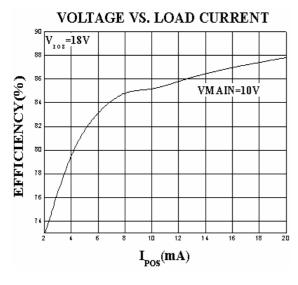

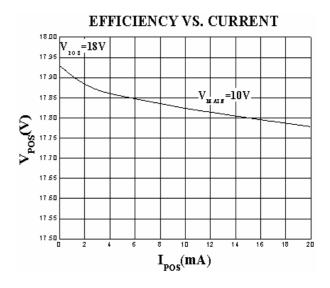

## EFFICIENCY VS. LOAD CURRENT

DS2618 Ver0.1 Nov. 2007

# **Preliminary**

$V_{POS}$ =18 $V_{POS}$ =10mA

# KTTIC

### **Detailed Description**

#### **Main Boost Converter Operations**

In steady state operating and continuous conduction mode where the inductor current is continuous, the boost converter operates in two cycles. During the first cycle, the internal power FET turns on and the Schottky diode is reverse biased and cuts off the current flow to the output. The output current is supplied from the output capacitor. The voltage across the inductor is VIN and the inductor current ramps up in a rate of VIN/L, L is the inductance. The inductance is magnetized and energy is stored in the inductor. The change in inductor current is:

$$\Delta I_{L} = \Delta T2 \times \frac{V_{IN} - V_{MAIN}}{L}$$

$$\Delta T2 = \frac{1 - D}{F_{LX}}$$

For stable operation, the same amount of energy stored in the inductor must be taken out. The change in inductor current during the two cycles must be the same.

$\Delta I1 + \Delta I2 = 0$

$$\frac{D}{F_{LX}} \times \frac{V_{IN}}{L} + \frac{1-D}{F_{LX}} \times \frac{V_{IN} - V_{MAIN}}{L} = 0$$

$$\frac{V_{MAIN}}{V_{IN}} = \frac{1}{1 - D}$$

#### **Output Voltage**

An external feedback resistor divider is required to divide the output voltage down to the nominal 1.25V reference voltage. The current drawn by the resistor network should be limited to maintain the overall converter efficiency. The maximum value of the resistor network is limited by the feedback input bias current and the potential for noise being coupled into the feedback pin. Selecting  $R_2$  in the range of  $10k\Omega$  to  $50\ k\Omega$ . The boost converter output voltage s determined by the relationship:

$$V_{\text{MAIN}} = V_{\text{FB}} \times \left[ 1 + \frac{R_1}{R_2} \right]$$

The nominal VFB voltage is 1.25V

#### **Dual Charge-Pump Regulator**

The EUP2618 contain two individual low-power charge pumps. One charge pump inverts the supply voltage (SUPN) and provides a regulated negative output voltage. The second charge pump doubles the supply voltage (SUPP) and provides a regulated positive output voltage. The EUP2618 contain internal p-channel and n-channel MOSFETs to control the power transfer. The internal MOSFETs switch at a constant 600kHz (0.5 x  $f_{\rm OSC}$ ).

#### **Negative Charge Pump**

During the first half-cycle, the p-channel MOSFET turns on and the flying capacitor C5 charges to  $V_{SUPN}$  minus a diode drop. During the second half-cycle, the p-channel MOSFET turns off, and the n-channel MOSFET turns on, level shifting C5. This connects C5 in parallel with the reservoir capacitor C6. If the voltage across C6 minus a diode drop is lower than the voltage across C5, charge flows from C5 to C6 until the diode (D5) turns off. The amount of charge transferred to the output is controlled by the variable n-channel on-resistance.

#### **Positive Charge Pump**

During the first half-cycle, the n-channel MOSFET turns on and charges the flying capacitor C3. This initial charge is controlled by the variable n-channel on resistance. During the second half-cycle, the n-channel MOSFET turns off and the p-channel MOSFET turns on, level shifting C3 by  $V_{SUPP}$  volts. This connects C3 in parallel with the reservoir capacitor C4. If the voltage across C4 plus a diode drop ( $V_{POS} + V_{DIODE}$ ) is smaller than the level-shifted flying capacitor voltage ( $V_{C3} + V_{SUPP}$ ), charge flows from C3 to C4 until the diode (D3) turns off.

#### Shutdown

A logic-low level on SHDN disables all three EUP2618 converters and the reference. When shut down, supply current drops to 0.1µA to maximize battery life and the reference is pulled to ground. The output capacitance and load current determine the rate at which each output voltage will decay. A logic-level high on SHDN power activates the EUP2618 (see the Power-Up Sequencing section). Do not leave SHDN floating. If unused, connect SHDN to GND.

#### **Power-Up Sequencing**

Upon power-up or exiting shutdown, the EUP2618 start their respective power-up sequences.

The reference powers up first, then the main DC-DC step-up converter powers up with softstart enabled. Once the main step-up converter reaches regulation, the negative charge pump turns on. The positive charge pump starts up. Finally, when the positive output voltage reaches 88% of its nominal value ( $V_{FBP} > 1.1V$ ), the active-low ready signal ( $\overline{RDY}$ ) goes low (see the *Power Ready* section).

#### **Power Ready**

Power ready is an open-drain output. When the power up sequence is properly completed, the MOSFET turns on and pulls RDY low with a typical  $125\Omega$  on-resistance. If a fault is detected, the internal open-drain MOSFET appears as a high impedance. Connect a  $100k\Omega$  pullup resistor between RDY and IN for a logic level output.

#### **Fault Detection**

Once  $\overline{RDY}$  is low and  $\overline{if}$  any output falls below its fault-detection threshold,  $\overline{RDY}$  goes high impedance.

For the main boost converter, the fault threshold is 88% of its nominal value ( $V_{FB} < 1.1V$ ). For the negative charge pump, the fault threshold is approximately 90% of its nominal value ( $V_{FBN} < 130 mV$ ). For the positive charge pump, the fault threshold is 88% of its nominal value ( $V_{FBP} < 1.1V$ ).

Once an output faults, all outputs later in the power sequence shut down until the faulted output rises above its power-up threshold.

#### **Inductor Selection**

The inductor selection determines the output ripple voltage, transient response, output current capability, and efficiency. Its selection depends on the input voltage, output voltage, switching frequency, and maximum output current. For most applications, a 4.7µH to 10uH inductor is recommended for 1.2MHz application. The inductor maximum DC current specification must be greater than the peak inductor current required by the regulator. The peak inductor current can be calculated:

$$I_{L(PEAK)} = \frac{I_{MAIN} \times V_{MAIN}}{V_{IN}} + 1/2 \times \frac{V_{IN} \times (V_{MAIN} - V_{IN})}{L \times V_{MAIN} \times FREQ}$$

#### **Output Capacitor**

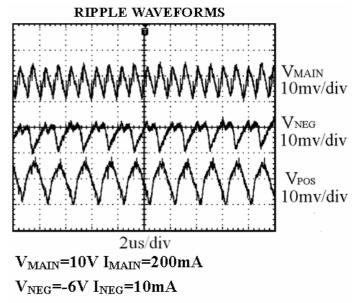

Low ESR capacitors should be used to minimized the output voltage ripple. Multilayer ceramic capacitors (X5R and X7R) are preferred for the output capacitors because of their lower ESR and small packages. Tantalum capacitors with higher ESR can also be used. The output ripple can be calculated as:

$$\Delta V_{O} = \frac{I_{MAIN} \times D}{F_{LX} \times C_{O}} + I_{MAIN} \times ESR$$

Choose an output capacitor to satisfy the output ripple and load transient requirement. A  $10\mu F$  to  $22\mu F$  ceramic capacitor is suitable for most application.

For noise sensitive application, a  $0.1\mu F$  placed in parallel with the larger output capacitor is recommended to reduce the switching noise coupled from the LX switching node.

#### **Input Capacitor**

The value of the input capacitor depends the input and output voltages, the maximum output current, the inductor value and the noise allowed to put back on the input line. For most applications, a minimum  $10\mu F$  is required. For applications that run close to the maximum output current limit, input capacitor in the range of  $22\mu F$  to  $47\mu F$  is recommended. The EUP2618 is powered from the VIN. High frequency  $0.1\mu F$  by-pass cap is recommended to be close to the VIN pin to reduce supply line noise and ensure stable operation.

#### **Rectifier Diode**

Use a Schottky diode with an average current rating equal to or greater than the peak inductor current, and a voltage rating at least 1.5 times the main output voltage  $(V_{MAIN})$ .

#### **Charge Pump**

#### **Efficiency Considerations**

The efficiency characteristics of the EUP2618 regulated charge pumps are similar to a linear regulator. They are dominated by quiescent current at low output currents and by the input voltage at higher output currents (see the Typical Operating Characteristics). So the maximum efficiency can be approximated by:

Efficiency

$$\cong V_{NEG}/[V_{SUPN} \times N];$$

for the negative charge pump

Efficiency  $\cong V_{POS}/[V_{SUPP} \times (N+1)];$

for the positive charge pump

where N is the number of charge-pump stages.

#### **Output Voltage Selection**

Adjust the positive output voltage by connecting a voltage-divider from the output ( $V_{POS}$ ) to FBP to GND (see the Typical Operating Circuit). Adjust the negative output voltage by connecting a voltage-divider from the output ( $V_{NEG}$ ) to FBN to REF. Select R4 and R6 in the  $50k\Omega$  to  $100k\Omega$  range. Higher resistor values improve efficiency at low output current but increase output-voltage error due to the feedback input bias current. Calculate the remaining resistors with the following equations:

$$R3 = R4[(V_{POS}/V_{REF}) - 1]$$

$$R5 = R6(V_{POS}/V_{REF})$$

where  $V_{REF} = 1.25V$ .  $V_{POS}$  can range from  $V_{SUPP}$  to 40V, and  $V_{NEG}$  can range from 0 to -40V.

#### **Flying Capacitor**

Increasing the flying capacitor's value reduces the output current capability. Above a certain point, increasing the capacitance has a negligible effect because the output current capability becomes dominated by the internal switch resistance and the diode impedance. Start with  $0.1 \mu F$  ceramic capacitors. Smaller values can be used for low-current applications.

#### **Charge-Pump Output Capacitor**

Increasing the output capacitance or decreasing the ESR reduces the output ripple voltage and the peak-to-peak transient voltage. Use the following equation to approximate the required capacitor value:

$$C_{OUT} \ge [I_{OUT}/(600 \text{kHz} \times V_{RIPPLE})]$$

Use a bypass capacitor with a value equal to or greater than the flying capacitor. Place the capacitor as close to the IC as possible. Connect directly to TGND.

#### **Charge-Pump Input Capacitor**

Use a bypass capacitor with a value equal to or greater than the flying capacitor. Place the capacitor as close to the IC as possible. Connect directly to GND.

#### **Rectifier Diode**

Use Schottky diodes with a current rating equal to or greater than 4 times the average output current, and a voltage rating at least 1.5 times  $V_{\text{SUPP}}$  for the positive charge pump and  $V_{\text{SUPN}}$  for the negative charge pump.

#### **PC Board Layout and Grounding**

Careful printed circuit layout is extremely important to minimize ground bounce and noise. First, place the main boost-converter output diode and output capacitor less than 0.2in (5mm) from the LX and PGND pins with wide traces and no vias. Then place 0.1µF ceramic bypass capacitors near the charge-pump input pins (SUPP and SUPN) to the PGND pin. Keep the charge pump circuitry as close to the IC as possible, using wide traces and avoiding vias when possible. Locate all feedback resistive dividers as close to their respective feedback pins as possible. The PC board should feature separate GND and PGND areas connected at only one point under the IC. To maximize output power and efficiency and to minimize output-power ripple voltage, use extra wide power ground traces and solder the IC's power ground pin directly to it. Avoid having sensitive traces near the switching nodes and high-current lines.

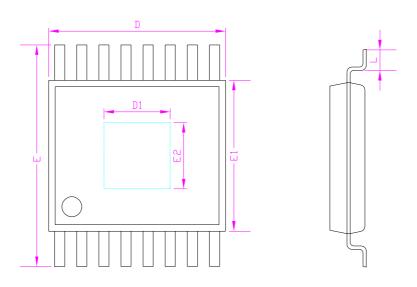

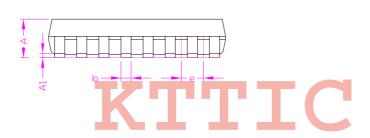

# **Packaging Information**

TSSOP-16

| SYMBOLS | MILLIN | METERS | INCHES |       |  |

|---------|--------|--------|--------|-------|--|

| STMBOLS | MIN.   | MAX.   | MIN.   | MAX.  |  |

| A       | -      | 1.20   | -      | 0.047 |  |

| A1      | 0.00   | 0.15   | 0.000  | 0.006 |  |

| b       | 0.19   | 0.30   | 0.007  | 0.012 |  |

| E1      | 4.     | 40     | 0.173  |       |  |

| D       | 5.00   |        | 0.197  |       |  |

| Е       | 6.20   | 6.60   | 0.244  | 0.260 |  |

| e       | 0.65   |        | 0.026  |       |  |

| L       | 0.45   | 0.75   | 0.018  | 0.030 |  |