54LS645 / 74LS645 LSTTL型八总线收发器(三态、原码)

- 三态输出直接驱动总线

- PNP输入减小了直流负载

- 输入滞后电压可改善噪声容限

- 典型参数 tpd=8ns Pd=310mW

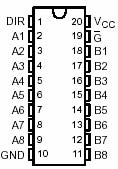

外引线排列图

功能表

| 使能 | 方向控制 | 操作 |

| L | L | B数据到 A总线 |

| L | H | A数据到 B总线 |

| H | X | 隔离 |

H=高电平 L=低电平 X=不定

说明:

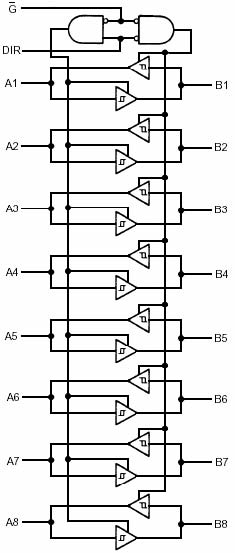

这种八位总线收发器是为数据总线间进行异步两路通讯而设计的。采用控制功能可以尽量减少外部定时电路的要求。

这种电路可以将数据从 A总线传送到 B总线,也可将数据从 B总线传送到 A总线,具体传送方向要看方向控制( DIR)输入的逻辑电平而定。可以用使能输入![]() 来禁止这种电路,使总线之间能有效地隔离。

来禁止这种电路,使总线之间能有效地隔离。

推荐工作条件

| 符号 | 参数名称 | 74LS645 | 54LS645 | 单位 | ||||

|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | 最小 | 典型 | 最大 | |||

| Vcc | 电源电压 | 4.75 | 5 | 5.25 | 4.5 | 5 | 5.5 | V |

| VIH | 输入高电平电压 | 2.0 | 2.0 | V | ||||

| VIL | 输入低电平电压 | 0.6 | 0.5 | V | ||||

| IOH | 输出高电平电流 | -15 | -12 | mA | ||||

| IOL | 输出低电平电流 | 24 | 12 | mA | ||||

| TA | 工作环境温度 | -40 | 85 | -55 | 125 | ℃ | ||

电 性 能:(除特别说明外,均为全温度范围)

| 符号 | 参数名称 | 测试条件 | 74LS645 | 54LS645 | 单位 | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | 最小 | 典型 | 最大 | |||||||

| VIK | 输入钳位电压 | Vcc=最小 II=-18mA | -1.5 | -1.5 | V | |||||||

| VT+-VT | 滞后电压 | Vcc=最小 | 0.2 | 0.4 | 0.2 | 0.4 | V | |||||

| VOH | 输出高电平电压 | Vcc=最小 VIL =最大 VIH=2V IOH =-3mA | 2.4 | 3.1 | 2.4 | 3.1 | V | |||||

| Vcc=最小 VIL =最大 VIH=2V IOH =最大 | 2.0 | 2.0 | V | |||||||||

| VOL | 输出低电平电压 | Vcc=最小 VIL=最大 VIH=2V IOL=最大 | 0.35 | 0.5 | 0.25 | 0.4 | V | |||||

| II | 输入电流 | A或B | Vcc=最大 | VI=7V | 0.1 | 0.1 | mA | |||||

| 或 DIR | VI=5.5V | 0.1 | 0.1 | |||||||||

| IIH | 输入高电平电流 | Vcc=最大 VI=2.7V | 20 | 20 | μA | |||||||

| IIL | 输入低电平电流 | Vcc=最大 VI=0.4V | -0.4 | -0.4 | mA | |||||||

| IOZH | 高关态输出电流 | Vcc=最大接 2.0V VIL =最大 Vo=2.7V | 20 | 20 | μA | |||||||

| IOZL | 低关态输出电流 | Vcc=最大接 2.0V VIL=最大 Vo=0.4V | -400 | -400 | μA | |||||||

| IOS | 输出短路电流 | Vcc=最大 Vo=0V | -40 | -225 | -40 | -225 | mA | |||||

| ICCH | 高电平电源电流 | Vcc=最大 | 输出为高 | 70 | 48 | 70 | mA | |||||

| ICCL | 低电平电源电流 | 输出开路 | 输出为低 | 90 | 62 | 90 | mA | |||||

| ICCZ | 禁态电源电流 | 输出禁态 | 95 | 64 | 95 | mA | ||||||

注:所有典型值均在 Vcc=5.0V, TA=25℃下测量得出。

交流(开关)参数:Vcc=5.0V, TA=25℃

| 符号 | 参数名称 | 从(输入) | 到(输出) | 测试条件 | 参数值 | 单位 | ||

|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | ||||||

| tPLH | 传输延迟 | A | B | 8 | 15 | ns | ||

| B | A | 8 | 15 | |||||

| tPHL | 传输延迟 | A | B | CL=45pF | 11 | 15 | ns | |

| B | A | 11 | 15 | |||||

| tPZL | 传输延迟 | , DIR | A | RL=667Ω | 31 | 40 | ns | |

| , DIR | B | 31 | 40 | |||||

| tPZH | 传输延迟 | , DIR | A | 26 | 40 | ns | ||

| , DIR | B | 26 | 40 | |||||

| tPLZ | 传输延迟 | , DIR | A | CL=5pF | 15 | 25 | ns | |

| , DIR | B | 15 | 25 | |||||

| tPHZ | 传输延迟 | , DIR | A | RL=667Ω | 15 | 25 | ns | |

| , DIR | B | 15 | 25 | |||||